Field-programmable gate array

Encyclopedia

Integrated circuit

An integrated circuit or monolithic integrated circuit is an electronic circuit manufactured by the patterned diffusion of trace elements into the surface of a thin substrate of semiconductor material...

designed to be configured by the customer or designer after manufacturing—hence "field-programmable". The FPGA configuration is generally specified using a hardware description language

Hardware description language

In electronics, a hardware description language or HDL is any language from a class of computer languages, specification languages, or modeling languages for formal description and design of electronic circuits, and most-commonly, digital logic...

(HDL), similar to that used for an application-specific integrated circuit

Application-specific integrated circuit

An application-specific integrated circuit is an integrated circuit customized for a particular use, rather than intended for general-purpose use. For example, a chip designed solely to run a cell phone is an ASIC...

(ASIC) (circuit diagram

Circuit diagram

A circuit diagram is a simplified conventional graphical representation of an electrical circuit...

s were previously used to specify the configuration, as they were for ASICs, but this is increasingly rare).

FPGAs can be used to implement any logical function that an ASIC could perform. The ability to update the functionality after shipping, partial re-configuration

Partial re-configuration

Partial Reconfiguration is the process of configuring a portion of a field programmable gate array while the other part is still running/operating....

of the portion of the design and the low non-recurring engineering costs relative to an ASIC design (notwithstanding the generally higher unit cost), offer advantages for many applications.

FPGAs contain programmable logic

Programmable logic device

A programmable logic device or PLD is an electronic component used to build reconfigurable digital circuits. Unlike a logic gate, which has a fixed function, a PLD has an undefined function at the time of manufacture...

components called "logic blocks", and a hierarchy of reconfigurable interconnects that allow the blocks to be "wired together"—somewhat like many (changeable) logic gates that can be inter-wired in (many) different configurations. Logic blocks can be configured to perform complex combinational functions

Combinational logic

In digital circuit theory, combinational logic is a type of digital logic which is implemented by boolean circuits, where the output is a pure function of the present input only. This is in contrast to sequential logic, in which the output depends not only on the present input but also on the...

, or merely simple logic gate

Logic gate

A logic gate is an idealized or physical device implementing a Boolean function, that is, it performs a logical operation on one or more logic inputs and produces a single logic output. Depending on the context, the term may refer to an ideal logic gate, one that has for instance zero rise time and...

s like AND

AND gate

The AND gate is a basic digital logic gate that implements logical conjunction - it behaves according to the truth table to the right. A HIGH output results only if both the inputs to the AND gate are HIGH . If neither or only one input to the AND gate is HIGH, a LOW output results...

and XOR

XOR gate

The XOR gate is a digital logic gate that implements an exclusive or; that is, a true output results if one, and only one, of the inputs to the gate is true . If both inputs are false or both are true , a false output results. Its behavior is summarized in the truth table shown on the right...

. In most FPGAs, the logic blocks also include memory elements, which may be simple flip-flops

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic...

or more complete blocks of memory.

In addition to digital functions, some FPGAs have analog features.

The most common analog feature is programmable slew rate

Slew rate

In electronics, the slew rate represents the maximum rate of change of a signal at any point in a circuit.Limitations in slew rate capability can give rise to non linear effects in electronic amplifiers...

and drive strength on each output pin,

allowing the engineer to set slow rates on lightly loaded pins that would otherwise ring

Electrical resonance

Electrical resonance occurs in an electric circuit at a particular resonance frequency where the imaginary parts of circuit element impedances or admittances cancel each other...

unacceptably, and to set stronger, faster rates on heavily loaded pins on high-speed channels that would otherwise run too slow.

Another relatively common analog feature is differential comparators on input pins designed to be connected to differential signaling

Differential signaling

Differential signaling is a method of transmitting information electrically by means of two complementary signals sent on two separate wires. The technique can be used for both analog signaling, as in some audio systems, and digital signaling, as in RS-422, RS-485, Ethernet , PCI Express and USB...

channels.

A few "mixed signal

Mixed-signal integrated circuit

A mixed-signal integrated circuit is any integrated circuit that has both analog circuits and digital circuits on a single semiconductor die.- Examples :...

FPGAs" have integrated peripheral Analog-to-Digital Converters (ADCs)

Analog-to-digital converter

An analog-to-digital converter is a device that converts a continuous quantity to a discrete time digital representation. An ADC may also provide an isolated measurement...

and Digital-to-Analog Converters (DACs)

Digital-to-analog converter

In electronics, a digital-to-analog converter is a device that converts a digital code to an analog signal . An analog-to-digital converter performs the reverse operation...

with analog signal conditioning blocks allowing them to operate as a system-on-a-chip

System-on-a-chip

A system on a chip or system on chip is an integrated circuit that integrates all components of a computer or other electronic system into a single chip. It may contain digital, analog, mixed-signal, and often radio-frequency functions—all on a single chip substrate...

.

Such devices blur the line between an FPGA, which carries digital ones and zeros on its internal programmable interconnect fabric,

and field-programmable analog array (FPAA), which carries analog values on its internal programmable interconnect fabric.

History

The FPGA industry sprouted from programmable read-only memoryProgrammable read-only memory

A programmable read-only memory or field programmable read-only memory or one-time programmable non-volatile memory is a form of digital memory where the setting of each bit is locked by a fuse or antifuse. Such PROMs are used to store programs permanently...

(PROM) and programmable logic devices (PLDs). PROMs and PLDs both had the option of being programmed in batches in a factory or in the field (field programmable), however programmable logic was hard-wired between logic gates.

In the late 1980s the Naval Surface Warfare Department funded an experiment proposed by Steve Casselman to develop a computer that would implement 600,000 reprogrammable gates. Casselman was successful and a patent related to the system was issued in 1992.

Some of the industry’s foundational concepts and technologies for programmable logic arrays, gates, and logic blocks are founded in patents awarded to David W. Page and LuVerne R. Peterson in 1985.

Xilinx

Xilinx

Xilinx, Inc. is a supplier of programmable logic devices. It is known for inventing the field programmable gate array and as the first semiconductor company with a fabless manufacturing model....

Co-Founders, Ross Freeman

Ross Freeman

Ross Freeman founded leading FPGA developer Xilinx in 1984 and a year later invented the first Field Programmable Gate Array. Freeman's invention - patent 4,870,302 - is a computer chip full of 'open gates' that engineers can reprogram as much as needed to add new functionality, adapt to changing...

and Bernard Vonderschmitt, invented the first commercially viable field programmable gate array in 1985 – the XC2064. The XC2064 had programmable gates and programmable interconnects between gates, the beginnings of a new technology and market. The XC2064 boasted a mere 64 configurable logic blocks (CLBs), with two 3-input lookup tables (LUTs). More than 20 years later, Freeman was entered into the National Inventors Hall of Fame

National Inventors Hall of Fame

The National Inventors Hall of Fame is a not-for-profit organization dedicated to recognizing, honoring and encouraging invention and creativity through the administration of its programs. The Hall of Fame honors the men and women responsible for the great technological advances that make human,...

for his invention.

Xilinx continued unchallenged and quickly growing from 1985 to the mid-1990s, when competitors sprouted up, eroding significant market-share. By 1993, Actel was serving about 18 percent of the market.

The 1990s were an explosive period of time for FPGAs, both in sophistication and the volume of production. In the early 1990s, FPGAs were primarily used in telecommunications and networking. By the end of the decade, FPGAs found their way into consumer, automotive, and industrial applications.

FPGAs got a glimpse of fame in 1997, when Adrian Thompson, a researcher working at the University of Sussex

University of Sussex

The University of Sussex is an English public research university situated next to the East Sussex village of Falmer, within the city of Brighton and Hove. The University received its Royal Charter in August 1961....

, merged genetic algorithm technology and FPGAs to create a sound recognition device. Thomson’s algorithm

Algorithm

In mathematics and computer science, an algorithm is an effective method expressed as a finite list of well-defined instructions for calculating a function. Algorithms are used for calculation, data processing, and automated reasoning...

configured an array of 10 x 10 cells in a Xilinx FPGA chip to discriminate between two tones, utilising analogue features of the digital chip. The application of genetic algorithms to the configuration of devices like FPGAs is now referred to as Evolvable hardware

Evolvable hardware

Evolvable hardware is a new field about the use of evolutionary algorithms to create specialized electronics without manual engineering. It brings together reconfigurable hardware, artificial intelligence, fault tolerance and autonomous systems...

Modern developments

A recent trend has been to take the coarse-grained architectural approach a step further by combining the logic blocks and interconnects of traditional FPGAs with embedded microprocessors and related peripherals to form a complete "system on a programmable chip". This work mirrors the architecture by Ron Perlof and Hana Potash of Burroughs Advanced Systems Group which combined a reconfigurable CPU architecture on a single chip called the SB24. That work was done in 1982. Examples of such hybrid technologies can be found in the Xilinx Virtex-II PRO and Virtex-4 devices, which include one or more PowerPCPowerPC

PowerPC is a RISC architecture created by the 1991 Apple–IBM–Motorola alliance, known as AIM...

processors embedded within the FPGA's logic fabric. The Atmel FPSLIC is another such device, which uses an AVR

Atmel AVR

The AVR is a modified Harvard architecture 8-bit RISC single chip microcontroller which was developed by Atmel in 1996. The AVR was one of the first microcontroller families to use on-chip flash memory for program storage, as opposed to one-time programmable ROM, EPROM, or EEPROM used by other...

processor in combination with Atmel's programmable logic architecture. The Actel SmartFusion devices incorporate an ARM architecture

ARM architecture

ARM is a 32-bit reduced instruction set computer instruction set architecture developed by ARM Holdings. It was named the Advanced RISC Machine, and before that, the Acorn RISC Machine. The ARM architecture is the most widely used 32-bit ISA in numbers produced...

Cortex-M3 hard processor core (with up to 512kB of flash and 64kB of RAM) and analog peripherals such as a multi-channel ADC and DACs to their flash-based FPGA fabric.

In 2010, an extensible processing platform was introduced for FPGAs that fused features of an ARM high-end microcontroller (hard-core implementations of a 32-bit processor, memory, and I/O) with an FPGA fabric to make FPGAs easier for embedded designers to use. By incorporating the ARM processor-based platform into a 28 nm FPGA family, the extensible processing platform enables system architects and embedded software developers to apply a combination of serial and parallel processing to address the challenges they face in designing today's embedded systems, which must meet ever-growing demands to perform highly complex functions. By allowing them to design in a familiar ARM environment, embedded designers can benefit from the time-to-market advantages of an FPGA platform compared to more traditional design cycles associated with ASICs.

An alternate approach to using hard-macro processors is to make use of soft processor core

Semiconductor intellectual property core

In electronic design a semiconductor intellectual property core, IP core, or IP block is a reusable unit of logic, cell, or chip layout design that is the intellectual property of one party. IP cores may be licensed to another party or can be owned and used by a single party alone...

s that are implemented within the FPGA logic. MicroBlaze

MicroBlaze

The MicroBlaze is a soft processor core designed for Xilinx FPGAs from Xilinx. As a soft-core processor, MicroBlaze is implemented entirely in the general-purpose memory and logic fabric of Xilinx FPGAs.-Overview:...

and Nios II

Nios II

Nios II is a 32-bit embedded-processor architecture designed specifically for the Altera family of FPGAs. Nios II incorporates many enhancements over the original Nios architecture, making it more suitable for a wider range of embedded computing applications, from DSP to system-control.Nios II is...

are examples of popular softcore processors.

As previously mentioned, many modern FPGAs have the ability to be reprogrammed at "run time," and this is leading to the idea of reconfigurable computing

Reconfigurable computing

Reconfigurable computing is a computer architecture combining some of the flexibility of software with the high performance of hardware by processing with very flexible high speed computing fabrics like field-programmable gate arrays...

or reconfigurable systems — CPUs

Central processing unit

The central processing unit is the portion of a computer system that carries out the instructions of a computer program, to perform the basic arithmetical, logical, and input/output operations of the system. The CPU plays a role somewhat analogous to the brain in the computer. The term has been in...

that reconfigure themselves to suit the task at hand. The Mitrion Virtual Processor from Mitrionics

Mitrionics

Mitrionics is a Swedish company manufacturing softcore reconfigurable processors. It has been mentioned as one of EETimes "60 Emerging startups".The company was founded in 2001 to commercialize a massively parallel reconfigurable processor implemented on FPGAs...

is an example of a reconfigurable soft processor, implemented on FPGAs. However, it does not support dynamic reconfiguration at runtime, but instead adapts itself to a specific program.

Additionally, new, non-FPGA architectures are beginning to emerge. Software-configurable microprocessor

Microprocessor

A microprocessor incorporates the functions of a computer's central processing unit on a single integrated circuit, or at most a few integrated circuits. It is a multipurpose, programmable device that accepts digital data as input, processes it according to instructions stored in its memory, and...

s such as the Stretch S5000 adopt a hybrid approach by providing an array of processor cores and FPGA-like programmable cores on the same chip.

Gates

- 1987: 9,000 gates, Xilinx

- 1992: 600,000, Naval Surface Warfare Department

- Early 2000s: Millions

Market size

- 1985: First commercial FPGA technology invented by Xilinx

- 1987: $14 million

- ~1993: >$385 million

- 2005: $1.9 billion

- 2010 estimates: $2.75 billion

FPGA comparisons

Historically, FPGAs have been slower, less energy efficient and generally achieved less functionality than their fixed ASICASIC

ASIC may refer to:* Application-specific integrated circuit, an integrated circuit developed for a particular use, as opposed to a customised general-purpose device.* ASIC programming language, a dialect of BASIC...

counterparts. A study has shown that designs implemented on FPGAs need on average 18 times as much area, draw 7 times as much dynamic power, and are 3 times slower than the corresponding ASIC implementations.

Advantages include the ability to re-program in the field to fix bugs, and may include a shorter time to market

Time to market

In commerce, time to market is the length of time it takes from a product being conceived until its being available for sale. TTM is important in industries where products are outmoded quickly...

and lower non-recurring engineering

Non-recurring engineering

Non-recurring engineering refers to the one-time cost to research, develop, design and test a new product. When budgeting for a project, NRE must be considered to analyze if a new product will be profitable...

costs. Vendors can also take a middle road by developing their hardware on ordinary FPGAs, but manufacture their final version so it can no longer be modified after the design has been committed.

Xilinx claims that several market and technology dynamics are changing the ASIC/FPGA paradigm:

- Integrated circuitIntegrated circuitAn integrated circuit or monolithic integrated circuit is an electronic circuit manufactured by the patterned diffusion of trace elements into the surface of a thin substrate of semiconductor material...

costs are rising aggressively - ASIC complexity has lengthened development time

- R&D resources and headcount are decreasing

- Revenue losses for slow time-to-market are increasing

- Financial constraints in a poor economy are driving low-cost technologies

These trends make FPGAs a better alternative than ASICs for a larger number of higher-volume applications than they have been historically used for, to which the company attributes the growing number of FPGA design starts (see History).

Some FPGAs have the capability of partial re-configuration

Partial re-configuration

Partial Reconfiguration is the process of configuring a portion of a field programmable gate array while the other part is still running/operating....

that lets one portion of the device be re-programmed while other portions continue running.

Versus complex programmable logic devices

The primary differences between CPLDCPLD

A complex programmable logic device is a programmable logic device with complexity between that of PALs and FPGAs, and architectural features of both. The building block of a CPLD is the macrocell, which contains logic implementing disjunctive normal form expressions and more specialized logic...

s (Complex Programmable Logic Devices) and FPGAs are architectural. A CPLD has a somewhat restrictive structure consisting of one or more programmable sum-of-products logic arrays feeding a relatively small number of clocked registers. The result of this is less flexibility, with the advantage of more predictable timing delays and a higher logic-to-interconnect ratio. The FPGA architectures, on the other hand, are dominated by interconnect. This makes them far more flexible (in terms of the range of designs that are practical for implementation within them) but also far more complex to design for.

In practice, the distinction between FPGAs and CPLDs is often one of size as FPGAs are usually much larger in terms of resources than CPLDs. Typically only FPGA's contain more advanced embedded functions such as adders, multipliers, memory, serdes

SerDes

A Serializer/Deserializer is a pair of functional blocks commonly used in high speed communications to compensate for limited input/output. These blocks convert data between serial data and parallel interfaces in each direction...

and other hardened functions. Another common distinction is that CPLDs contain embedded flash to store their configuration while FPGAs usually, but not always, require an external flash or other device to store their configuration.

Security considerations

With respect to security, FPGAs have both advantages and disadvantages as compared to ASICs or secure microprocessors. FPGAs' flexibility makes malicious modifications during fabrication a lower risk. For many FPGAs, the loaded design is exposed while it is loaded (typically on every power-on). To address this issue, some FPGAs support bitstream encryption., although in July 2011, researchers published papers highlighting vulnerabilities in the bitstream encryption of some devices related to the analysis of the device's power usage fluctuations.These vulnerabilities apply to the current devices of most FPGA manufacturers, including Altera and Xilinx.

Applications

Applications of FPGAs include digital signal processingDigital signal processing

Digital signal processing is concerned with the representation of discrete time signals by a sequence of numbers or symbols and the processing of these signals. Digital signal processing and analog signal processing are subfields of signal processing...

, software-defined radio

Software-defined radio

A software-defined radio system, or SDR, is a radio communication system where components that have been typically implemented in hardware are instead implemented by means of software on a personal computer or embedded computing devices...

, aerospace

Aerospace

Aerospace comprises the atmosphere of Earth and surrounding space. Typically the term is used to refer to the industry that researches, designs, manufactures, operates, and maintains vehicles moving through air and space...

and defense

Defense (military)

Defense has several uses in the sphere of military application.Personal defense implies measures taken by individual soldiers in protecting themselves whether by use of protective materials such as armor, or field construction of trenches or a bunker, or by using weapons that prevent the enemy...

systems, ASIC

Application-specific integrated circuit

An application-specific integrated circuit is an integrated circuit customized for a particular use, rather than intended for general-purpose use. For example, a chip designed solely to run a cell phone is an ASIC...

prototyping, medical imaging

Medical imaging

Medical imaging is the technique and process used to create images of the human body for clinical purposes or medical science...

, computer vision

Computer vision

Computer vision is a field that includes methods for acquiring, processing, analysing, and understanding images and, in general, high-dimensional data from the real world in order to produce numerical or symbolic information, e.g., in the forms of decisions...

, speech recognition

Speech recognition

Speech recognition converts spoken words to text. The term "voice recognition" is sometimes used to refer to recognition systems that must be trained to a particular speaker—as is the case for most desktop recognition software...

, cryptography

Cryptography

Cryptography is the practice and study of techniques for secure communication in the presence of third parties...

, bioinformatics

Bioinformatics

Bioinformatics is the application of computer science and information technology to the field of biology and medicine. Bioinformatics deals with algorithms, databases and information systems, web technologies, artificial intelligence and soft computing, information and computation theory, software...

, computer hardware emulation

Emulator

In computing, an emulator is hardware or software or both that duplicates the functions of a first computer system in a different second computer system, so that the behavior of the second system closely resembles the behavior of the first system...

, radio astronomy

Radio astronomy

Radio astronomy is a subfield of astronomy that studies celestial objects at radio frequencies. The initial detection of radio waves from an astronomical object was made in the 1930s, when Karl Jansky observed radiation coming from the Milky Way. Subsequent observations have identified a number of...

, metal detection and a growing range of other areas.

FPGAs originally began as competitors to CPLD

CPLD

A complex programmable logic device is a programmable logic device with complexity between that of PALs and FPGAs, and architectural features of both. The building block of a CPLD is the macrocell, which contains logic implementing disjunctive normal form expressions and more specialized logic...

s and competed in a similar space, that of glue logic

Glue logic

In electronics, glue logic is the custom logic circuitry used to interface a number of off-the-shelf integrated circuits.This is often achieved using ordinary 7400- or 4000-series components. In more complex cases, programmable logic devices like a CPLD or FPGA might be used...

for PCBs

Printed circuit board

A printed circuit board, or PCB, is used to mechanically support and electrically connect electronic components using conductive pathways, tracks or signal traces etched from copper sheets laminated onto a non-conductive substrate. It is also referred to as printed wiring board or etched wiring...

. As their size, capabilities, and speed increased, they began to take over larger and larger functions to the state where some are now marketed as full systems on chips (SoC

System-on-a-chip

A system on a chip or system on chip is an integrated circuit that integrates all components of a computer or other electronic system into a single chip. It may contain digital, analog, mixed-signal, and often radio-frequency functions—all on a single chip substrate...

). Particularly with the introduction of dedicated multipliers into FPGA architectures in the late 1990s, applications which had traditionally been the sole reserve of DSPs

Digital signal processor

A digital signal processor is a specialized microprocessor with an architecture optimized for the fast operational needs of digital signal processing.-Typical characteristics:...

began to incorporate FPGAs instead.

Traditionally, FPGAs have been reserved for specific vertical applications where the volume of production is small. For these low-volume applications, the premium that companies pay in hardware costs per unit for a programmable chip is more affordable than the development resources spent on creating an ASIC for a low-volume application. Today, new cost and performance dynamics have broadened the range of viable applications.

Applications in High Performance Computing

FPGAs are increasingly used in conventional high performance computing applications where computational kernels (Fast Fourier transformFast Fourier transform

A fast Fourier transform is an efficient algorithm to compute the discrete Fourier transform and its inverse. "The FFT has been called the most important numerical algorithm of our lifetime ." There are many distinct FFT algorithms involving a wide range of mathematics, from simple...

, convolution

Convolution

In mathematics and, in particular, functional analysis, convolution is a mathematical operation on two functions f and g, producing a third function that is typically viewed as a modified version of one of the original functions. Convolution is similar to cross-correlation...

etc) are performed on the FPGA instead of a microprocessor

Microprocessor

A microprocessor incorporates the functions of a computer's central processing unit on a single integrated circuit, or at most a few integrated circuits. It is a multipurpose, programmable device that accepts digital data as input, processes it according to instructions stored in its memory, and...

. FPGA implementation of these kernels offer order of magnitude performance improvements over microprocessors. Other benefits are in terms of power used: a FPGA implementation of FFT or convolution is expected to consume less power than in a microprocessor. Low-power usage is due to the lower clock rate and higher execution efficiency (microprocessors require additional cycles to preform instruction fetch & decode).

The inherent parallelism of the logic resources on an FPGA allows for considerable computational throughput even at a low MHz clock rates. The flexibility of the FPGA allows for even higher performance by trading off precision and range in the number format for an increased number of parallel arithmetic units. For example, a floating point adder takes too many FPGA resources (LUTs and Flip-Flops) as compared to a fixed point adder. However latest Xilinx Virtex-6 FPGAs may have as much as 2048 DSP blocks, allowing hundreds of floating point adders/multipliers.

Example applications:

An AES

AES

AES may refer to:Standards, systems, and methods* Application Environment Services, a component of Digital Research's GEM windowing system* The Advanced Encryption Standard...

encryption circuit implemented on a Xilinx

Xilinx

Xilinx, Inc. is a supplier of programmable logic devices. It is known for inventing the field programmable gate array and as the first semiconductor company with a fabless manufacturing model....

Virtex5 FPGA running at 100MHz may be 10 times faster than a highly optimized AES encryption running on a latest CPU. Similar performance improvements (order of magnitude or more) may be obtained for other computationally intensive applications like N-body simulation

N-body simulation

An N-body simulation is a simulation of a dynamical system of particles, usually under the influence of physical forces, such as gravity . In cosmology, they are used to study processes of non-linear structure formation such as the process of forming galaxy filaments and galaxy halos from dark...

, image processing

Image processing

In electrical engineering and computer science, image processing is any form of signal processing for which the input is an image, such as a photograph or video frame; the output of image processing may be either an image or, a set of characteristics or parameters related to the image...

and manipulation, image registration

Image registration

Image registration is the process of transforming different sets of data into one coordinate system. Data may be multiple photographs, data from different sensors, from different times, or from different viewpoints. It is used in computer vision, medical imaging, military automatic target...

etc.

The adoption of FPGAs in high performance computing is currently limited by the complexity of FPGA design compared to conventional software and the turn-around times of current design tools. Place and route for a complex design may take a day to succeed.

FPGAs especially find applications in any area or algorithm that can make use of the massive parallelism offered by their architecture. One such area is code breaking, in particular brute-force attack, of cryptographic algorithms.

Architecture

The most common FPGA architecture consists of an array of logic blocks (called Configurable Logic Block, CLB, or Logic Array Block, LAB, depending on vendor), I/O pads, and routing channels. Generally, all the routing channels have the same width (number of wires). Multiple I/O pads may fit into the height of one row or the width of one column in the array.An application circuit must be mapped into an FPGA with adequate resources. While the number of CLBs/LABs and I/Os required is easily determined from the design, the number of routing tracks needed may vary considerably even among designs with the same amount of logic. For example, a crossbar switch

Crossbar switch

In electronics, a crossbar switch is a switch connecting multiple inputs to multiple outputs in a matrix manner....

requires much more routing than a systolic array

Systolic array

In computer architecture, a systolic array is a pipe network arrangement of processing units called cells. It is a specialized form of parallel computing, where cells , compute data and store it independently of each other.thumb|240px...

with the same gate count. Since unused routing tracks increase the cost (and decrease the performance) of the part without providing any benefit, FPGA manufacturers try to provide just enough tracks so that most designs that will fit in terms of LUTs and IOs can be routed. This is determined by estimates such as those derived from Rent's rule

Rent's Rule

Rent's rule pertains to the organization of computing logic, specifically the relationship between the number of external signal connections to a logic block with the number of logic gates in the logic block, and has been applied to circuits ranging from small digital circuits to mainframe...

or by experiments with existing designs.

In general, a logic block (CLB or LAB) consists of a few logical cells (called ALM, LE, Slice etc.). A typical cell consists of a 4-input Lookup table (LUT), a Full adder (FA) and a D-type flip-flop

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic...

, as shown below. The LUTs are in this figure split into two 3-input LUTs. In normal mode those are combined into a 4-input LUT through the left mux

Multiplexer

In electronics, a multiplexer is a device that selects one of several analog or digital input signals and forwards the selected input into a single line. A multiplexer of 2n inputs has n select lines, which are used to select which input line to send to the output...

. In arithmetic mode, their outputs are fed to the FA. The selection of mode is programmed into the middle multiplexer. The output can be either synchronous or asynchronous, depending on the programming of the mux to the right, in the figure example. In practice, entire or parts of the FA are put as functions into the LUTs in order to save space.

ALMs and Slices usually contains 2 or 4 structures similar to the example figure, with some shared signals.

CLBs/LABs typically contains a few ALMs/LEs/Slices.

In recent years, manufacturers have started moving to 6-input LUTs in their high performance parts, claiming increased performance.

Since clock signals (and often other high-fanout

Fanout

In digital electronics, the fan-out of a logic gate output is the number of gate inputs to which it is connected.In most designs, logic gates are connected together to form more complex circuits. While no more than one logic gate output is connected to any single input, it is common for one output...

signals) are normally routed via special-purpose dedicated routing networks in commercial FPGAs, they and other signals are separately managed.

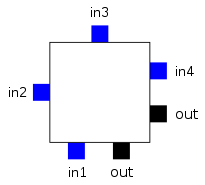

For this example architecture, the locations of the FPGA logic block pins are shown below.

Each logic block output pin can connect to any of the wiring segments in the channels adjacent to it.

Similarly, an I/O pad can connect to any one of the wiring segments in the channel adjacent to it. For example, an I/O pad at the top of the chip can connect to any of the W wires (where W is the channel width) in the horizontal channel immediately below it.

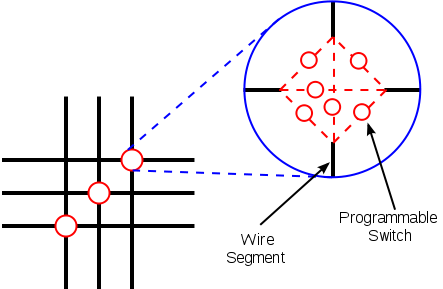

Generally, the FPGA routing is unsegmented. That is, each wiring segment spans only one logic block before it terminates in a switch box. By turning on some of the programmable switches within a switch box, longer paths can be constructed. For higher speed interconnect, some FPGA architectures use longer routing lines that span multiple logic blocks.

Whenever a vertical and a horizontal channel intersect, there is a switch box. In this architecture, when a wire enters a switch box, there are three programmable switches that allow it to connect to three other wires in adjacent channel segments. The pattern, or topology, of switches used in this architecture is the planar or domain-based switch box topology. In this switch box topology, a wire in track number one connects only to wires in track number one in adjacent channel segments, wires in track number 2 connect only to other wires in track number 2 and so on. The figure below illustrates the connections in a switch box.

FPGAs are also widely used for systems validation including pre-silicon validation, post-silicon validation, and firmware development. This allows chip companies to validate their design before the chip is produced in the factory, reducing the time-to-market.

To shrink the size and power consumption of FPGAs, vendors such as Tabula and Xilinx have introduced new 3D or stacked architectures. Following the introduction of its 28 nm 7-series FPGAs, Xilinx revealed that that several of the highest-density parts in those FPGA product lines will be constructed using multiple dice in one package, employing technology developed for 3D construction and stacked-die assemblies. The technology stacks several (three or four) active FPGA dice side-by-side on a silicon interposer – a single piece of silicon that carries passive interconnect.

FPGA design and programming

To define the behavior of the FPGA, the user provides a hardware description languageHardware description language

In electronics, a hardware description language or HDL is any language from a class of computer languages, specification languages, or modeling languages for formal description and design of electronic circuits, and most-commonly, digital logic...

(HDL) or a schematic

Schematic

A schematic diagram represents the elements of a system using abstract, graphic symbols rather than realistic pictures. A schematic usually omits all details that are not relevant to the information the schematic is intended to convey, and may add unrealistic elements that aid comprehension...

design. The HDL form is more suited to work with large structures because it's possible to just specify them numerically rather than having to draw every piece by hand. However, schematic entry can allow for easier visualisation of a design.

Then, using an electronic design automation

Electronic design automation

Electronic design automation is a category of software tools for designing electronic systems such as printed circuit boards and integrated circuits...

tool, a technology-mapped netlist

Netlist

The word netlist can be used in several different contexts, but perhaps the most popular is in the field of electronic design. In this context, a "netlist" describes the connectivity of an electronic design....

is generated. The netlist can then be fitted to the actual FPGA architecture using a process called place-and-route

Place and route

Place and route is a stage in the design of printed circuit boards, integrated circuits, and field-programmable gate arrays. As implied by the name, it is composed of two steps, placement and routing. The first step, placement, involves deciding where to place all electronic components, circuitry,...

, usually performed by the FPGA company's proprietary place-and-route software. The user will validate the map, place and route results via timing analysis, simulation

Simulation

Simulation is the imitation of some real thing available, state of affairs, or process. The act of simulating something generally entails representing certain key characteristics or behaviours of a selected physical or abstract system....

, and other verification

Verification and Validation

In software project management, software testing, and software engineering, verification and validation is the process of checking that a software system meets specifications and that it fulfills its intended purpose...

methodologies. Once the design and validation process is complete, the binary file generated (also using the FPGA company's proprietary software) is used to (re)configure the FPGA. This file is transferred to the FPGA/CPLD via a serial interface

Serial communication

In telecommunication and computer science, serial communication is the process of sending data one bit at a time, sequentially, over a communication channel or computer bus. This is in contrast to parallel communication, where several bits are sent as a whole, on a link with several parallel channels...

(JTAG) or to an external memory device like an EEPROM

EEPROM

EEPROM stands for Electrically Erasable Programmable Read-Only Memory and is a type of non-volatile memory used in computers and other electronic devices to store small amounts of data that must be saved when power is removed, e.g., calibration...

.

The most common HDLs are VHDL and Verilog

Verilog

In the semiconductor and electronic design industry, Verilog is a hardware description language used to model electronic systems. Verilog HDL, not to be confused with VHDL , is most commonly used in the design, verification, and implementation of digital logic chips at the register-transfer level...

, although in an attempt to reduce the complexity of designing in HDLs, which have been compared to the equivalent of assembly language

Assembly language

An assembly language is a low-level programming language for computers, microprocessors, microcontrollers, and other programmable devices. It implements a symbolic representation of the machine codes and other constants needed to program a given CPU architecture...

s, there are moves to raise the abstraction level through the introduction of alternative languages. National Instrument's LabVIEW

LabVIEW

LabVIEW is a system design platform and development environment for a visual programming language from National Instruments. LabVIEW provides engineers and scientists with the tools needed to create and deploy measurement and control systems.The graphical language is named "G"...

graphical programming language (sometimes referred to as "G") has an FPGA add-in module available to target and program FPGA hardware.

To simplify the design of complex systems in FPGAs, there exist libraries of predefined complex functions and circuits that have been tested and optimized to speed up the design process. These predefined circuits are commonly called IP core

Semiconductor intellectual property core

In electronic design a semiconductor intellectual property core, IP core, or IP block is a reusable unit of logic, cell, or chip layout design that is the intellectual property of one party. IP cores may be licensed to another party or can be owned and used by a single party alone...

s, and are available from FPGA vendors and third-party IP suppliers (rarely free, and typically released under proprietary licenses). Other predefined circuits are available from developer communities such as OpenCores

OpenCores

OpenCores is the world's largest open source hardware community developing digital open source hardware through electronic design automation, with a similar ethos to the free software movement. OpenCores hopes to eliminate redundant design work and slash development costs. A number of companies...

(typically released under free and open source

Free and open source software

Free and open-source software or free/libre/open-source software is software that is liberally licensed to grant users the right to use, study, change, and improve its design through the availability of its source code...

licenses such as the GPL

GNU General Public License

The GNU General Public License is the most widely used free software license, originally written by Richard Stallman for the GNU Project....

, BSD or similar license), and other sources.

In a typical design flow, an FPGA application developer will simulate the design at multiple stages throughout the design process. Initially the RTL

Register transfer level

In integrated circuit design, register-transfer level is a level of abstraction used in describing the operation of a synchronous digital circuit...

description in VHDL or Verilog

Verilog

In the semiconductor and electronic design industry, Verilog is a hardware description language used to model electronic systems. Verilog HDL, not to be confused with VHDL , is most commonly used in the design, verification, and implementation of digital logic chips at the register-transfer level...

is simulated by creating test benches to simulate the system and observe results. Then, after the synthesis

Logic synthesis

In electronics, logic synthesis is a process by which an abstract form of desired circuit behavior, typically register transfer level , is turned into a design implementation in terms of logic gates. Common examples of this process include synthesis of HDLs, including VHDL and Verilog...

engine has mapped the design to a netlist, the netlist is translated to a gate level description where simulation is repeated to confirm the synthesis proceeded without errors. Finally the design is laid out in the FPGA at which point propagation delays can be added and the simulation run again with these values back-annotated onto the netlist.

Basic process technology types

- SRAMStatic random access memoryStatic random-access memory is a type of semiconductor memory where the word static indicates that, unlike dynamic RAM , it does not need to be periodically refreshed, as SRAM uses bistable latching circuitry to store each bit...

- based on static memory technology. In-system programmable and re-programmable. Requires external boot devices. CMOSCMOSComplementary metal–oxide–semiconductor is a technology for constructing integrated circuits. CMOS technology is used in microprocessors, microcontrollers, static RAM, and other digital logic circuits...

. - AntifuseAntifuseAn antifuse is an electrical device that performs the opposite function to a fuse. Whereas a fuse starts with a low resistance and is designed to permanently break an electrically conductive path , an antifuse starts with a high resistance and is designed to permanently create an electrically...

- One-time programmable. CMOS. - PROMProgrammable read-only memoryA programmable read-only memory or field programmable read-only memory or one-time programmable non-volatile memory is a form of digital memory where the setting of each bit is locked by a fuse or antifuse. Such PROMs are used to store programs permanently...

- Programmable Read-Only Memory technology. One-time programmable because of plastic packaging. - EPROMEPROMAn EPROM , or erasable programmable read only memory, is a type of memory chip that retains its data when its power supply is switched off. In other words, it is non-volatile. It is an array of floating-gate transistors individually programmed by an electronic device that supplies higher voltages...

- Erasable Programmable Read-Only Memory technology. One-time programmable but with window, can be erased with ultraviolet (UV) light. CMOS. - EEPROMEEPROMEEPROM stands for Electrically Erasable Programmable Read-Only Memory and is a type of non-volatile memory used in computers and other electronic devices to store small amounts of data that must be saved when power is removed, e.g., calibration...

- Electrically Erasable Programmable Read-Only Memory technology. Can be erased, even in plastic packages. Some but not all EEPROM devices can be in-system programmed. CMOS. - FlashFlash memoryFlash memory is a non-volatile computer storage chip that can be electrically erased and reprogrammed. It was developed from EEPROM and must be erased in fairly large blocks before these can be rewritten with new data...

- Flash-erase EPROM technology. Can be erased, even in plastic packages. Some but not all flash devices can be in-system programmed. Usually, a flash cell is smaller than an equivalent EEPROM cell and is therefore less expensive to manufacture. CMOS. - FuseFuse (electrical)In electronics and electrical engineering, a fuse is a type of low resistance resistor that acts as a sacrificial device to provide overcurrent protection, of either the load or source circuit...

- One-time programmable. Bipolar.

Major manufacturers

XilinxXilinx

Xilinx, Inc. is a supplier of programmable logic devices. It is known for inventing the field programmable gate array and as the first semiconductor company with a fabless manufacturing model....

and Altera

Altera

Altera Corporation is a Silicon Valley manufacturer of PLDs . The company offered its first programmable logic device in 1984. PLDs can be reprogrammed during the design cycle as well as in the field to perform multiple functions, and they support a fairly fast design process...

are the current FPGA market leaders and long-time industry rivals. Together, they control over 80 percent of the market, with Xilinx alone representing over 50 percent.

Both Xilinx and Altera provide free Windows

Microsoft Windows

Microsoft Windows is a series of operating systems produced by Microsoft.Microsoft introduced an operating environment named Windows on November 20, 1985 as an add-on to MS-DOS in response to the growing interest in graphical user interfaces . Microsoft Windows came to dominate the world's personal...

and Linux

Linux

Linux is a Unix-like computer operating system assembled under the model of free and open source software development and distribution. The defining component of any Linux system is the Linux kernel, an operating system kernel first released October 5, 1991 by Linus Torvalds...

design software which provides limited set of devices.

Other competitors include Lattice Semiconductor

Lattice Semiconductor

Lattice Semiconductor Corporation is a United States based manufacturer of high-performance programmable logic devices . Founded in 1983, the company employs about 700 people and has annual revenues of around $300 million, with Darin Billerbeck as the chief executive officer...

(SRAM based with integrated configuration Flash, instant-on, low power, live reconfiguration), Actel

Actel

Actel Corporation is a manufacturer of nonvolatile, low-power FPGAs, mixed-signal FPGAs, and programmable logic solutions...

(antifuse, flash-based, mixed-signal), SiliconBlue Technologies

SiliconBlue Technologies

SiliconBlue Technologies Corporation is a United States based manufacturer of ultra-low power programmable logic devices that the company calls "mobile FPGAs." The products target mobile and hand-held electronics applications that require low power and small physical size..SiliconBlue iCEcube2...

(extremely low power SRAM-based FPGAs with option integrated nonvolatile configuration memory), Achronix (RAM based, 1.5 GHz fabric speed) who will be building their chips on Intels' state-of-the art 22 nm process, and QuickLogic

QuickLogic

QuickLogic Corporation is a manufacturer of Customer Specific Standard Products, or CSSP.Until 2007 they were a supplier of Field-Programmable Gate Arrays based on antifuse technology, making the devices one-time programmable...

(handheld focused CSSP, no general purpose FPGAs).

In March 2010, Tabula announced their new FPGA technology that uses time-multiplexed logic and interconnect for greater potential cost savings for high-density applications.

See also

- Gate arrayGate arrayA gate array or uncommitted logic array is an approach to the design and manufacture of application-specific integrated circuits...

- PSoCPSoCPSoC is a family of integrated circuits made by Cypress Semiconductor. These chips include a CPU and mixed-signal arrays of configurable integrated analog and digital peripherals.- History :...

- Application-specific integrated circuitApplication-specific integrated circuitAn application-specific integrated circuit is an integrated circuit customized for a particular use, rather than intended for general-purpose use. For example, a chip designed solely to run a cell phone is an ASIC...

(ASIC) - Application-specific instruction-set processorApplication-specific instruction-set processorAn application-specific instruction-set processor is a component used in system-on-a-chip design. The instruction set of an ASIP is tailored to benefit a specific application. This specialization of the core provides a tradeoff between the flexibility of a general purpose CPU and the performance...

(ASIP) - Impulse CoDeveloper (Impulse C)Impulse CImpulse C is a subset of the C programming language combined with a C-compatible function library supporting parallel programming, in particular for programming of applications targeting FPGA devices...

- Combinational logicCombinational logicIn digital circuit theory, combinational logic is a type of digital logic which is implemented by boolean circuits, where the output is a pure function of the present input only. This is in contrast to sequential logic, in which the output depends not only on the present input but also on the...

- Complex programmable logic device (CPLD)

- Erasable programmable logic device (EPLD)

- Software Defined SiliconSoftware Defined SiliconSoftware Defined Silicon is a computer chip technology created by XMOS of Bristol . XMOS was jointly-founded in 2005 by INMOS transputer architect David May. Software Defined Silicon is the name given to the family of multithreaded multicore on-chip processors that XMOS is developing....

(SDS) - Soft processor

- FPGA prototypeFPGA prototypeFPGA prototyping, sometimes also referred to as ASIC prototyping or SoC prototyping is the method to prototype SoC and ASIC design on FPGA forhardware verification and early software development....

- VHDLVHSIC Hardware Description LanguageVHDL is a hardware description language used in electronic design automation to describe digital and mixed-signal systems such as field-programmable gate arrays and integrated circuits.- History :...

: VHSICVHSICVHSIC was a 1980s U.S. government program to develop very-high-speed integrated circuits.The United States Department of Defense launched the VHSIC project in 1980 as a joint tri-service project. The project led to advances in integrated circuit materials, lithography, packaging, testing, and...

(Very High Speed Integrated Circuit) Hardware Description Language - VerilogVerilogIn the semiconductor and electronic design industry, Verilog is a hardware description language used to model electronic systems. Verilog HDL, not to be confused with VHDL , is most commonly used in the design, verification, and implementation of digital logic chips at the register-transfer level...

: Hardware Description Language - JHDLJHDLJHDL is a low-level structural hardware description language, focused primarily on building circuits via an Object Oriented approach that bundles collections of gates into Java objects...

: Just-Another Hardware Description Language - Reconfigurable computingReconfigurable computingReconfigurable computing is a computer architecture combining some of the flexibility of software with the high performance of hardware by processing with very flexible high speed computing fabrics like field-programmable gate arrays...

- Partial re-configurationPartial re-configurationPartial Reconfiguration is the process of configuring a portion of a field programmable gate array while the other part is still running/operating....

- Hybrid-core computingHybrid-core computingHybrid-core computing is the technique of extending a commodity instruction set architecture with application-specific instructions to accelerate application performance...

- Configware

- MyHDLMyHDLMyHDL is a Python based hardware description language .Features of MyHDL include:* The ability to generate VHDL and Verilog code from a MyHDL design....

Python based HDL—generates Verilog or VHDL - SystemCSystemCSystemC is a set of C++ classes and macros which provide an event-driven simulation kernel in C++ . These facilities enable a designer to simulate concurrent processes, each described using plain C++ syntax...

System Description Language—C like - Handel-CHandel-CHandel-C is a high level programming language which targets low-level hardware, most commonly used in the programming of FPGAs. It is a rich subset of C, with non-standard extensions to control hardware instantiation with an emphasis on parallelism. Handel-C is to hardware design what the first...

Extended C based description language designed for FPGAs - MinimigMinimigMinimig is an open source re-implementation of an Amiga 500 using a field-programmable gate array .Minimig started in secrecy around January 2005 as a proof of concept by Dutch electrical engineer Dennis van Weeren...

open source re-implementation of an Amiga 500 using an FPGA - Computing with MemoryComputing with MemoryComputing with Memory refers to computing platforms where function response is stored in memory array, either one or two-dimensional, in the form of lookup tables and functions are evaluated by retrieving the values from the LUTs...

A time-multiplexed reconfigurable architecture using 2-D memory array - Digital Clock ManagerDigital Clock ManagerDigital Clock Manager is a function for manipulating clock signals by: * Multiply and divide an incoming clock .* Recondition a clock to, for example, ensure 50% duty cycle.* Phase shift .* Eliminate clock skew.-See also:* Clock signal...

DCM - Digital Clock Management - Multi-gigabit transceiverMulti-gigabit transceiverA Multi-Gigabit Transceiver is a SerDes capable of operating at serial bit rates above 1 Gigabit/second. MGTs are used increasingly for data communications because they can run over longer distances, use fewer wires, and thus have lower costs than parallel interfaces with equivalent data...

or SerdesSerDesA Serializer/Deserializer is a pair of functional blocks commonly used in high speed communications to compensate for limited input/output. These blocks convert data between serial data and parallel interfaces in each direction...

- Serial transceivers now becoming very common in the FPGA fabric