Control register

Encyclopedia

A control register is a processor register

which changes or controls the general behavior of a CPU

or other digital device. Common tasks performed by control registers include interrupt

control, switching the addressing mode

, paging

control, and coprocessor

control.

and higher processors. On x86-64

processors in long mode

, it (and the other control registers) are 64 bits long. CR0 has various control flags that modify the basic operation of the processor.

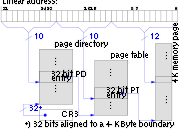

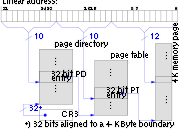

Used when virtual addressing

Used when virtual addressing

is enabled, hence when the PG bit is set in CR0. CR3 enables the processor to translate virtual addresses into physical addresses by locating the page directory and page table

s for the current task. Typically, the upper 20 bits of CR3 become the page directory base register (PDBR), which stores the physical address of the first page directory entry.

s.

processor, to allow enabling the SYSCALL/SYSRET instruction, and later for entering and exiting long mode

.

Processor register

In computer architecture, a processor register is a small amount of storage available as part of a CPU or other digital processor. Such registers are addressed by mechanisms other than main memory and can be accessed more quickly...

which changes or controls the general behavior of a CPU

Central processing unit

The central processing unit is the portion of a computer system that carries out the instructions of a computer program, to perform the basic arithmetical, logical, and input/output operations of the system. The CPU plays a role somewhat analogous to the brain in the computer. The term has been in...

or other digital device. Common tasks performed by control registers include interrupt

Interrupt

In computing, an interrupt is an asynchronous signal indicating the need for attention or a synchronous event in software indicating the need for a change in execution....

control, switching the addressing mode

Addressing mode

Addressing modes are an aspect of the instruction set architecture in most central processing unit designs. The various addressing modes that are defined in a given instruction set architecture define how machine language instructions in that architecture identify the operand of each instruction...

, paging

Paging

In computer operating systems, paging is one of the memory-management schemes by which a computer can store and retrieve data from secondary storage for use in main memory. In the paging memory-management scheme, the operating system retrieves data from secondary storage in same-size blocks called...

control, and coprocessor

Coprocessor

A coprocessor is a computer processor used to supplement the functions of the primary processor . Operations performed by the coprocessor may be floating point arithmetic, graphics, signal processing, string processing, or encryption. By offloading processor-intensive tasks from the main processor,...

control.

CR0

The CR0 register is 32 bits long on the 386Intel 80386

The Intel 80386, also known as the i386, or just 386, was a 32-bit microprocessor introduced by Intel in 1985. The first versions had 275,000 transistors and were used as the central processing unit of many workstations and high-end personal computers of the time...

and higher processors. On x86-64

X86-64

x86-64 is an extension of the x86 instruction set. It supports vastly larger virtual and physical address spaces than are possible on x86, thereby allowing programmers to conveniently work with much larger data sets. x86-64 also provides 64-bit general purpose registers and numerous other...

processors in long mode

Long mode

In the x86-64 computer architecture, long mode is the mode where a 64-bit application can access 64-bit instructions and registers...

, it (and the other control registers) are 64 bits long. CR0 has various control flags that modify the basic operation of the processor.

| Bit | Name | Full Name | Description |

|---|---|---|---|

| 31 | PG | Paging | If 1, enable paging and use the CR3 register, else disable paging |

| 30 | CD | Cache CPU cache A CPU cache is a cache used by the central processing unit of a computer to reduce the average time to access memory. The cache is a smaller, faster memory which stores copies of the data from the most frequently used main memory locations... disable |

Globally enables/disable the memory cache |

| 29 | NW | Not-write through | Globally enables/disable write-back caching |

| 18 | AM | Alignment mask | Alignment check enabled if AM set, AC flag (in EFLAGS FLAGS register (computing) The FLAGS register is the status register in Intel x86 microprocessors that contains the current state of the processor. This register is 16 bits wide. Its successors, the EFLAGS and RFLAGS registers, are 32 bits and 64 bits wide, respectively... register) set, and privilege level is 3 |

| 16 | WP | Write protect | Determines whether the CPU can write to pages marked read-only |

| 5 | NE | Numeric error | Enable internal x87 X87 x87 is a floating point-related subset of the x86 architecture instruction set. It originated as an extension of the 8086 instruction set in the form of optional floating point coprocessors that worked in tandem with corresponding x86 CPUs. These microchips had names ending in "87"... floating point error reporting when set, else enables PC style x87 error detection |

| 4 | ET | Extension type | On the 386, it allowed to specify whether the external math coprocessor was an 80287 or 80387 |

| 3 | TS | Task switched | Allows saving x87 task context only after x87 instruction used after task switch |

| 2 | EM | Emulation | If set, no x87 floating point unit Floating point unit A floating-point unit is a part of a computer system specially designed to carry out operations on floating point numbers. Typical operations are addition, subtraction, multiplication, division, and square root... present, if clear, x87 FPU present |

| 1 | MP | Monitor co-processor | Controls interaction of WAIT/FWAIT instructions with TS flag in CR0 |

| 0 | PE | Protected Mode Enable | If 1, system is in protected mode Protected mode In computing, protected mode, also called protected virtual address mode, is an operational mode of x86-compatible central processing units... , else system is in real mode Real mode Real mode, also called real address mode, is an operating mode of 80286 and later x86-compatible CPUs. Real mode is characterized by a 20 bit segmented memory address space and unlimited direct software access to all memory, I/O addresses and peripheral hardware... |

CR2

Contains a value called Page Fault Linear Address (PFLA). When a page fault occurs, the address the program attempted to access is stored in the CR2 register.CR3

Virtual memory

In computing, virtual memory is a memory management technique developed for multitasking kernels. This technique virtualizes a computer architecture's various forms of computer data storage , allowing a program to be designed as though there is only one kind of memory, "virtual" memory, which...

is enabled, hence when the PG bit is set in CR0. CR3 enables the processor to translate virtual addresses into physical addresses by locating the page directory and page table

Page table

A page table is the data structure used by a virtual memory system in a computer operating system to store the mapping between virtual addresses and physical addresses. Virtual addresses are those unique to the accessing process...

s for the current task. Typically, the upper 20 bits of CR3 become the page directory base register (PDBR), which stores the physical address of the first page directory entry.

CR4

Used in protected mode to control operations such as virtual-8086 support, enabling I/O breakpoints, page size extension and machine check exceptionMachine Check Exception

A Machine Check Exception is a type of computer hardware error that occurs when a computer's central processing unit detects a hardware problem....

s.

| Bit | Name | Full Name | Description |

|---|---|---|---|

| 18 | OSXSAVE | XSAVE and Processor Extended States Enable | |

| 17 | PCIDE | PCID Enable | If set, enables process-context identifiers (PCIDs). |

| 14 | SMXE | SMX Enable | |

| 13 | VMXE | VMX Enable | |

| 10 | OSXMMEXCPT | Operating System Support for Unmasked SIMD Floating-Point Exceptions | If set, enables unmasked SSE exceptions. |

| 9 | OSFXSR | Operating system support for FXSAVE and FXSTOR instructions | If set, enables SSE Streaming SIMD Extensions In computing, Streaming SIMD Extensions is a SIMD instruction set extension to the x86 architecture, designed by Intel and introduced in 1999 in their Pentium III series processors as a reply to AMD's 3DNow! . SSE contains 70 new instructions, most of which work on single precision floating point... instructions and fast FPU save & restore |

| 8 | PCE | Performance-Monitoring Counter enable | If set, RDPMC can be executed at any privilege level, else RDPMC can only be used in ring 0. |

| 7 | PGE | Page Global Enabled | If set, address translations (PDE or PTE records) may be shared between address spaces. |

| 6 | MCE | Machine Check Exception | If set, enables machine check interrupts to occur. |

| 5 | PAE | Physical Address Extension Physical Address Extension In computing, Physical Address Extension is a feature to allow x86 processors to access a physical address space larger than 4 gigabytes.... |

If set, changes page table layout to translate 32-bit virtual addresses into extended 36-bit physical addresses. |

| 4 | PSE | Page Size Extensions | If unset, page size is 4 KB, else page size is increased to 4 MB (ignored with PAE set). |

| 3 | DE | Debugging Extensions | |

| 2 | TSD | Time Stamp Disable | If set, RDTSC Time Stamp Counter The Time Stamp Counter is a 64-bit register present on all x86 processors since the Pentium. It counts the number of ticks since reset. The instruction "RDTSC" returns the TSC in EDX:EAX. In x86_64 mode, RDTSC also clears the higher 32 bits of RAX. Its opcode is 0F 31. Pentium competitors such as... instruction can only be executed when in ring 0, otherwise RDTSC can be used at any privilege level. |

| 1 | PVI | Protected-mode Virtual Interrupts | If set, enables support for the virtual interrupt flag (VIF) in protected mode. |

| 0 | VME | Virtual 8086 Mode Extensions | If set, enables support for the virtual interrupt flag (VIF) in virtual-8086 mode. |

EFER

Extended Feature Enable Register (EFER) is a register added in the AMD K6AMD K6

The K6 microprocessor was launched by AMD in 1997. The main advantage of this particular microprocessor is that it was designed to fit into existing desktop designs for Pentium branded CPUs. It was marketed as a product which could perform as well as its Intel Pentium II equivalent but at a...

processor, to allow enabling the SYSCALL/SYSRET instruction, and later for entering and exiting long mode

Long mode

In the x86-64 computer architecture, long mode is the mode where a 64-bit application can access 64-bit instructions and registers...

.

| Bit | Purpose |

|---|---|

| 63:12 | Reserved |

| 11 | Execute-disable bit enable (NXE) |

| 10 | IA-32e mode active (LMA) |

| 9 | Reserved |

| 8 | IA-32e mode enable (LME) |

| 7:1 | Reserved |

| 0 | SysCall enable (SCE) |

See also

- Protected mode in x86 Assembly at Wikibooks

- General purpose registersProcessor registerIn computer architecture, a processor register is a small amount of storage available as part of a CPU or other digital processor. Such registers are addressed by mechanisms other than main memory and can be accessed more quickly...

- Test registerTest registerA test register, in the Intel 80486 processor, is a register used by the processor, usually to do a self-test. Most of these registers are undocumented, and used by specialized software. The test registers were named TR3 to TR7. Regular programs don't usually require these registers to work...

- Debug register

- Flag byte

- Status registerStatus registerA status register or flag register is a collection of flag bits for a processor. An example is the FLAGS register of the x86 architecture....