.gif)

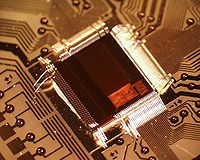

Beetle (ASIC)

Encyclopedia

Application-specific integrated circuit

An application-specific integrated circuit is an integrated circuit customized for a particular use, rather than intended for general-purpose use. For example, a chip designed solely to run a cell phone is an ASIC...

is an analog readout chip. It is developed for the LHCb

LHCb

LHCb is one of six particle physics detector experiments collecting data at the Large Hadron Collider accelerator at CERN. LHCb is a specialized b-physics experiment, that is measuring the parameters of CP violation in the interactions of b-hadrons...

experiment at CERN

CERN

The European Organization for Nuclear Research , known as CERN , is an international organization whose purpose is to operate the world's largest particle physics laboratory, which is situated in the northwest suburbs of Geneva on the Franco–Swiss border...

.

Overview

The chip integrates 128 channels with low-noise charge-sensitive pre-amplifiers and shapers. The pulse shape can be chosen such that it complies with LHCbLHCb

LHCb is one of six particle physics detector experiments collecting data at the Large Hadron Collider accelerator at CERN. LHCb is a specialized b-physics experiment, that is measuring the parameters of CP violation in the interactions of b-hadrons...

specifications: a peaking time of 25 ns with a remainder of the peak voltage after 25 ns of less than 30%. A comparator per channel with configurable polarity provides a binary signal. Four adjacent comparator channels are being OR

Logical disjunction

In logic and mathematics, a two-place logical connective or, is a logical disjunction, also known as inclusive disjunction or alternation, that results in true whenever one or more of its operands are true. E.g. in this context, "A or B" is true if A is true, or if B is true, or if both A and B are...

ed and brought off chip via LVDS drivers.

Either the shaper or comparator output is sampled with the LHC bunch-crossing frequency of 40 MHz into an analog pipeline. This ring buffer has a programmable latency of a maximum of 160 sampling intervals and an integrated derandomising buffer of 16 stages. For analogue readout data is multiplexed with up to 40 MHz onto one or four ports. A binary readout mode operates at up to 80 MHz output rate on two ports. Current drivers bring the serialised data off chip.

The chip can accept trigger rates up to 1.1 MHz to perform a dead-timeless readout within 900 ns per trigger. For testability and calibration purposes, a charge injector with adjustable pulse height is implemented. The bias settings and various other parameters can be controlled via a standard I²C

I²C

I²C is a multi-master serial single-ended computer bus invented by Philips that is used to attach low-speed peripherals to a motherboard, embedded system, cellphone, or other electronic device. Since the mid 1990s, several competitors I²C ("i-squared cee" or "i-two cee"; Inter-Integrated Circuit;...

-interface. The chip is radiation hardened to an accumulated dose of more than 100 Mrad

Rad (unit)

The rad is a unit of absorbed radiation dose. The rad was first proposed in 1918 as "that quantity of X rays which when absorbed will cause the destruction of the malignant mammalian cells in question..." It was defined in CGS units in 1953 as the dose causing 100 ergs of energy to be absorbed by...

. Robustness against single event upset

Single event upset

A single event upset is a change of state caused by ions or electro-magnetic radiation striking a sensitive node in a micro-electronic device, such as in a microprocessor, semiconductor memory, or power transistors. The state change is a result of the free charge created by ionization in or close...

is achieved by redundant logic.